In a recent study conducted by scientists from Tokyo Tech, two groundbreaking design techniques were introduced to significantly enhance the performance of fractional-N phase locked loops (PLLs). These methods were developed to combat fractional spurs, which are unwanted signals that commonly affect PLLs used in various radar systems and wireless transceivers. The implications of these advancements are substantial, as they could revolutionize wireless communication, autonomous vehicles, surveillance, and tracking systems in the post-5G era.

The smooth operation of wireless data transceivers and radar systems is crucial for emerging technologies like self-driving vehicles and target tracking systems. These systems rely heavily on the accurate synthesis, modulation, and synchronization of oscillating signals, all of which are facilitated by phase locked loops (PLLs). Therefore, mitigating errors and minimizing sources of interference in PLLs are essential for optimizing the overall performance of these systems.

Fractional-N PLLs are favored for their excellent resolution and flexible frequency control. However, they are plagued by issues such as jitter and fractional spurs. Jitter refers to deviations from the ideal timing of oscillations, while fractional spurs are unwanted signals that result from errors in the system. Digital-to-time converters (DTCs) are typically used in digital PLLs to counter quantization error, but imperfections in DTCs can lead to fractional spurs that degrade output quality.

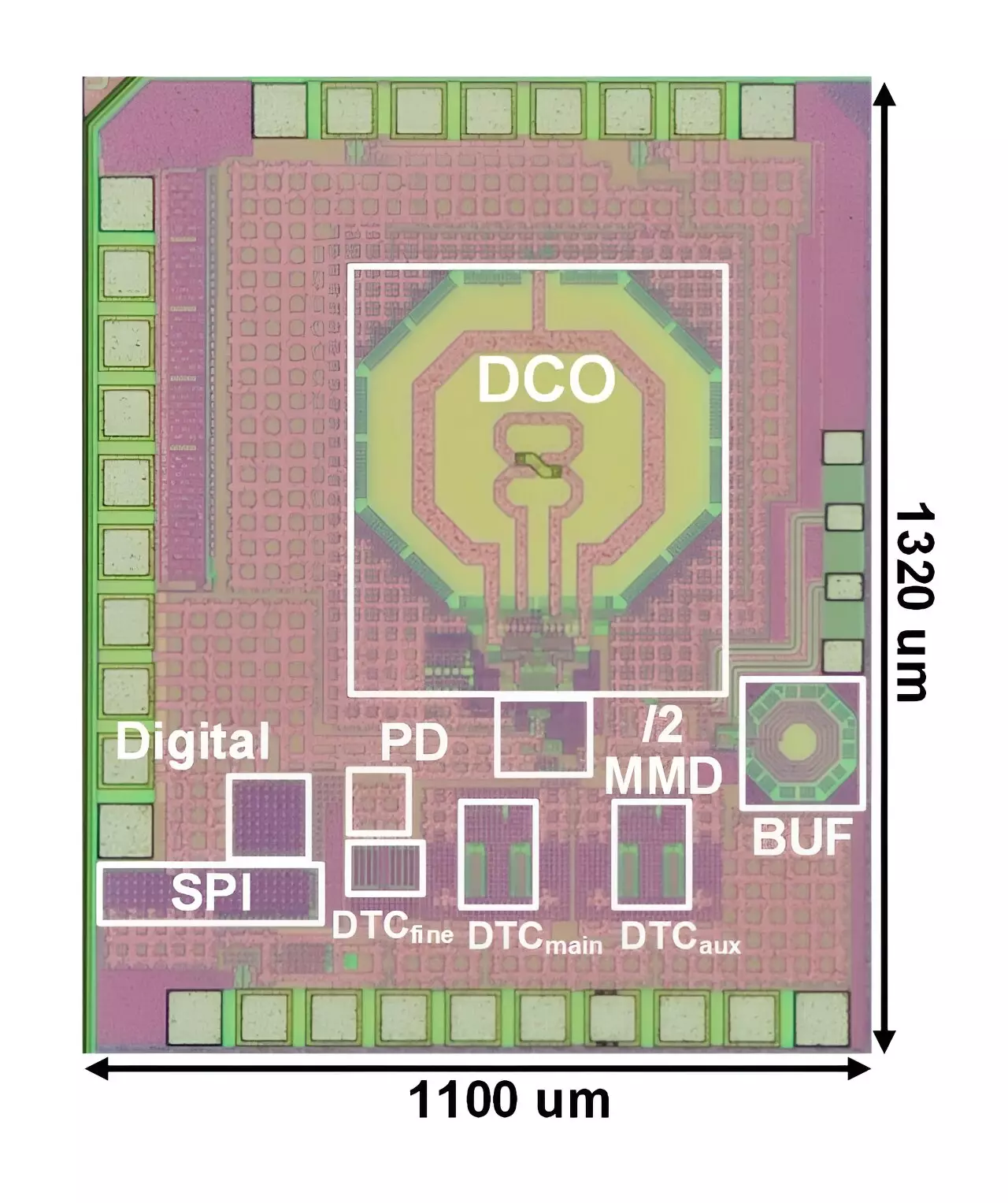

The research team at Tokyo Institute of Technology, led by Professor Kenichi Okada, devised two novel design techniques to address these challenges. The first technique involves using a cascaded-fractional divider to split the frequency control word (FCW) into two values that are far from integers. This approach filters out high-frequency components, reducing the impact of fractional spurs without the need for digital pre-distortion (DPD).

The second technique centers around a pseudo-differential DTC design that overcomes the limitations of traditional implementations. By leveraging the even-symmetric components of DTC non-linearities, the researchers used two half-range DTCs in differential operation to cancel out INLs at the PLL’s phase detector. This innovative approach allows for minimal fractional-spur levels, ultimately improving overall performance.

The team successfully implemented the proposed design using a 65nm CMOS process, requiring a compact circuit area of only 0.23 mm2. Compared to state-of-the-art designs, their device demonstrated significant advantages, including a reduction in integrated PLL jitter from 243.5 fs to 143.7 fs. The cascaded fractional divider and pseudo-differential DTC techniques employed by the researchers enabled superior performance without the need for DPD technology.

These innovative design techniques have the potential to drive advancements in various applications where fractional-N PLLs play a critical role. By minimizing fractional spurs and improving PLL performance, this research paves the way for enhanced wireless communication, autonomous systems, surveillance technology, and beyond.

Leave a Reply